This repository was archived by the owner on Jan 27, 2024. It is now read-only.

ЛР 6 для ИВТ. Управления регистром mepc и проблемы с поддержкой адреса mscratch в памяти #52

Unanswered

mrz25

asked this question in

Вопросы и ответы

Replies: 1 comment 9 replies

-

|

Если честно, не понял весь этот поток сознания, можете переформулировать?) |

Beta Was this translation helpful? Give feedback.

9 replies

Sign up for free

to join this conversation on GitHub.

Already have an account?

Sign in to comment

Uh oh!

There was an error while loading. Please reload this page.

-

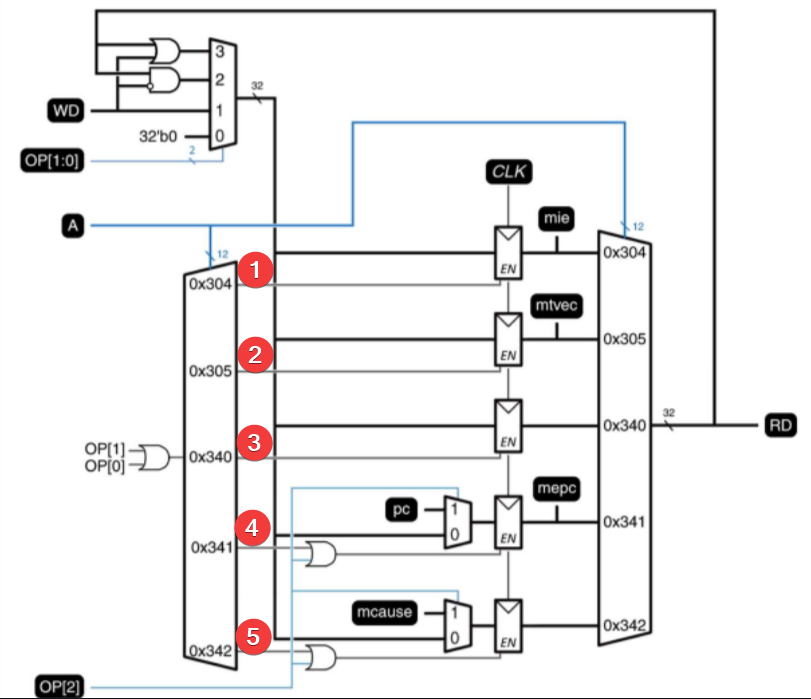

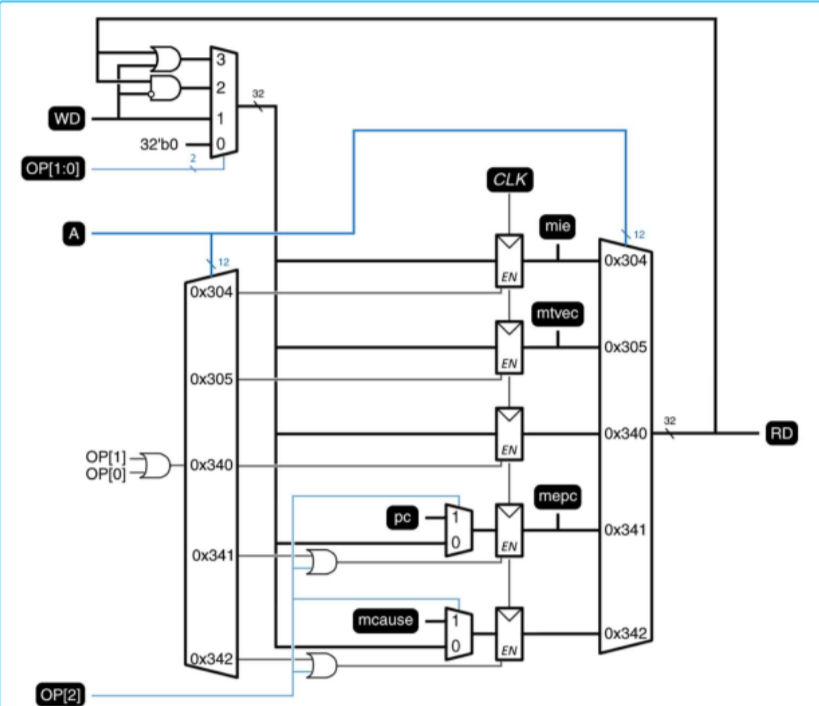

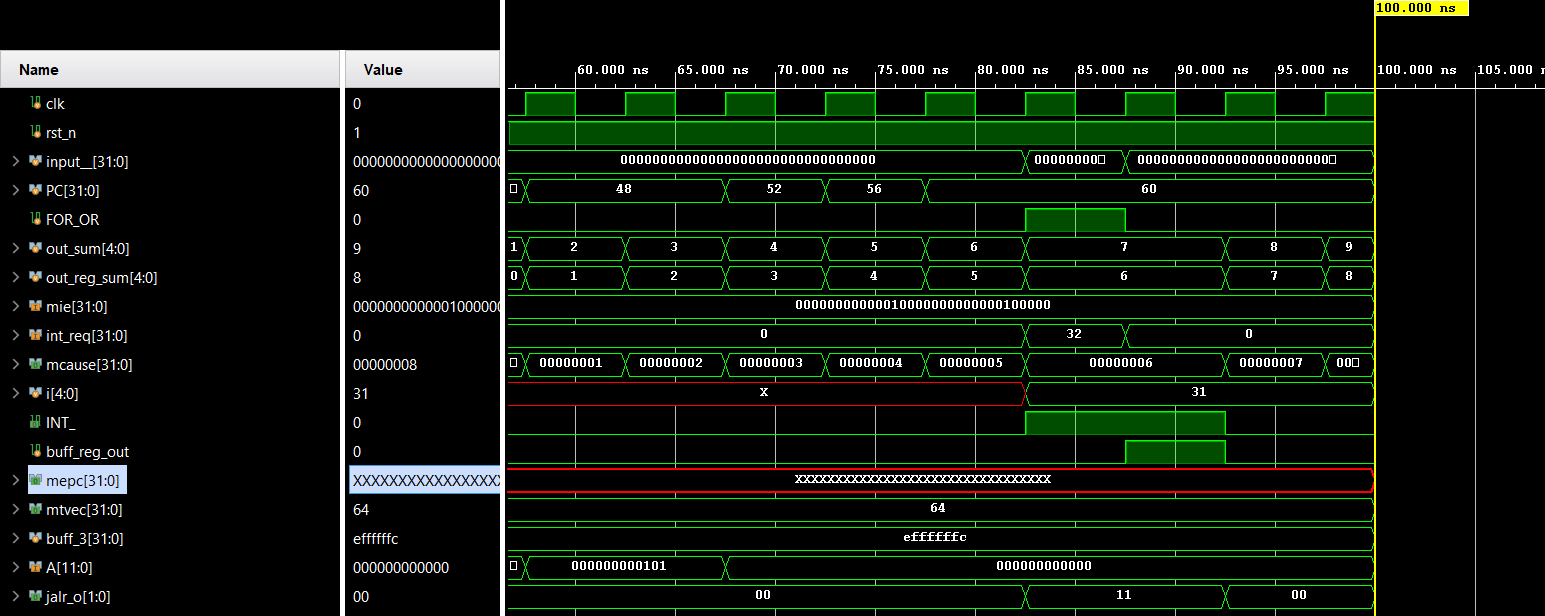

Тестирую свою реализацию системы прерываний, и встал вопрос, вот у нас прошли первоначальные присваивания да, потом начинается бесконечный цикл, в процессе которого, через такт, я посылаю int_req = 32, то есть на 5 вход прерывания, которое прописано и сигнал INT_ поднимается c interrapt_controller'a и посылается на декодер, соответственно мы по идее должны обработать этот сигнал и записать в mepc <= PC, а в PC <= mtvec вроде как в один такт, но не суть, если мы хотим это сделать, то встал вопрос - как записать mepc <= PC, и если csr, CSROp и jalr_o мы можем выставить для всего этого, но нам вроде как адрес с команды должен прийти, а он не контролируется декодером... и что делать... или я чего-то не понимаю?

Beta Was this translation helpful? Give feedback.

All reactions