This repository was archived by the owner on Jan 27, 2024. It is now read-only.

Replies: 1 comment 4 replies

-

|

Попробуй следующий листинг: reg [1:0] state;

localparam IDLE = 2'd0;

localparam RECEIVE_DATA = 2'd1;

localparam CHECK_PARITY_STOP_BITS = 2'd2;

always @(posedge clk_50 or posedge areset) begin

if(areset)

state <= IDLE;

else if (ps2_clk_negedge)

begin

case (state)

IDLE:

begin

if(!ps2_dat)

state <= RECEIVE_DATA;

end

RECEIVE_DATA:

begin

if (count_bit == 8)

state <=

CHECK_PARITY_STOP_BITS;

end

CHECK_PARITY_STOP_BITS:

begin

state <= IDLE;

end

default:

begin

state <= IDLE;

end

endcase

end

end

|

Beta Was this translation helpful? Give feedback.

4 replies

Sign up for free

to join this conversation on GitHub.

Already have an account?

Sign in to comment

Uh oh!

There was an error while loading. Please reload this page.

-

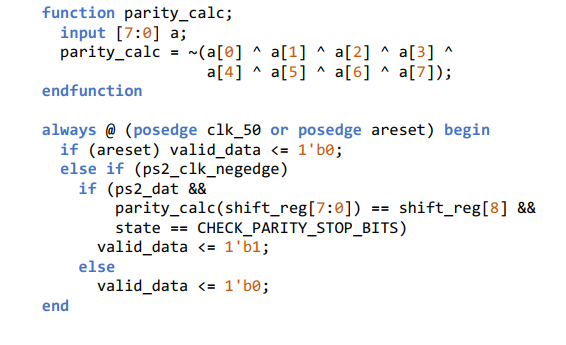

В лабораторной предлагается код конечного автомата для контроллера клавиатуры по интерфейсу PS/2.

При использовании этого кода возникла проблема: автомат переходил в состояние CHECK_PARITY_STOP_BITS в момент, когда еще необходимо было принимать данные, связано это с тем, что инкрементация counter_bit начинается с старт бита, который нам принимать в сдвиговый регистр не нужно, из-за этого последний бит данных не записывается в сдвиговый регистр.

Также нам необходимо в конце принять в сдвиговый регистр бит четности, но опять же автомат переходит в состояние CHECK_PARITY_STOP_BITS и не записывает его.

Для решения этих багов предлагаю в конечном автомате изменить условие перехода в состояние CHECK_PARITY_STOP_BITS на

(count_bit == 10)На временной диаграмме передаю контроллеру клавиатуры код клавиши - 0x3a. Как видно из диаграммы, менять состояние на CHECK_PARITY_STOP_BITS необходимо при counter_bit = 10, к этому моменту в сдвиговый регистр приняты данные 0x3a и бит четности = 1

Beta Was this translation helpful? Give feedback.

All reactions