SDR design based on the AT86RF215 transceiver with IQ LVDS / FPGA DDR (dual-data-rate) interface. The quadrature data is clocked on the rising and falling edges. Ethernet is 100Mbps. The firmware and HDL was written and operational in 2018. It supports stand-alone reception of P25. The firmware implementation is P25 P1 only. It does not currently do P25 P2 or P25 trunk-tracking, but the hardware is capable. It can also be used with SDR software over Ethernet such as GQRX with modified RTL-TCP drivers (mods allow 16-bit samples).

To compile:

install the gcc arm toolchain version gcc-arm-none-eabi-7-2018-q2-update/

https://developer.arm.com/tools-and-software/open-source-software/developer-tools/gnu-toolchain/gnu-rm/downloads/7-2018-q2-update

In the firmware directory, create a symbolic link to the toolchain:

e.g. ln -s ../gcc-arm-none-eabi-7-2018-q2-update arm-toolchain

Then type 'make'

To compile the verilog code and place-route for the FPGA, you will need to install project ice-storm,Yosys, and nextpnr. In order to run the testbench for the DDR verilog code, you will also need to install iverilog and gtkwave.

https://github.com/YosysHQ/icestorm

https://github.com/YosysHQ/yosys

https://github.com/YosysHQ/nextpnr

https://github.com/steveicarus/iverilog

https://github.com/gtkwave/gtkwave

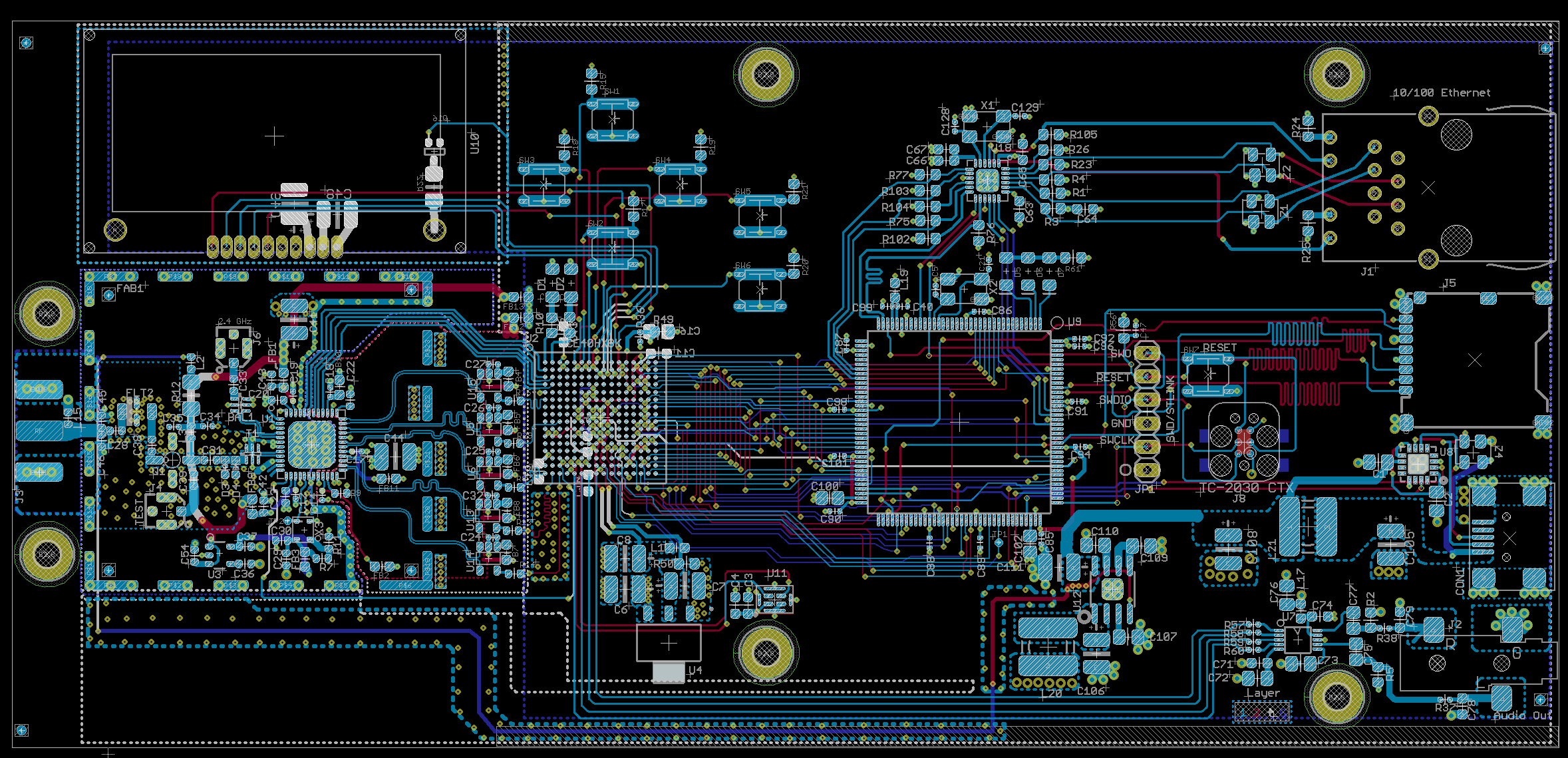

AT86RF215 12-bit I/Q Receiver PCB / ICE40 BGA-256 FPGA / STM32H743 MCU / 100Mbps Ethernet / Stereo I2S Audio

Dual-antenna VHF/UHF Tuner PCB (1MHz to 1200 MHz), IF output is 914 MHz and fed to the AT86RF215 receiver.

FPGA Routing / Usage